使用EYEQ特性实现高速串行IO的最佳相位接收判决

简介

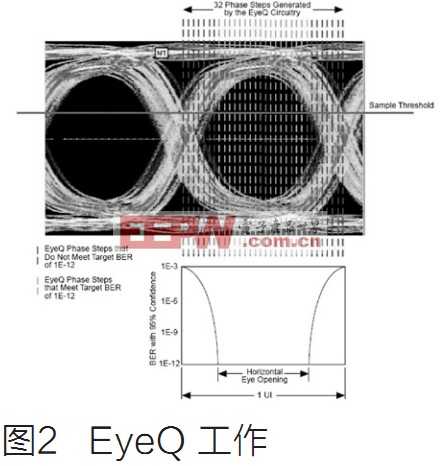

现有的很多高速串口协议,都要求很低的误码率,比如CEI-6G-LR(6.375G, 40英寸走线)就要求1E-15的误码率。为满足此类低误码率要求,ALTERA高端的FPGA STRATIX IV系列,提供了片上信号质量检测电路(EYEQ),帮助客户在高速串行IO接收处找到最优的采样位置。

买芯片网专注整合全球优质Altera代理商现货资源,是国内领先的Altera(英特尔)、Lattice(莱迪思)、Xilinx(赛灵思 AMD)芯片采购服务平台,买芯片网轻松满足您的芯片采购需求.

通常眼图的张开度是用来衡量接收端信号的质量。片上信号质量检测电路(EYEQ)就是一个调试诊断工具来帮助分析接收的数据路径,包括接收端的增益,噪声水平。

原理

缺省情况下,CDR恢复时钟是在眼图的中间位置采数据,。

Altera中国海量优质的信息资源、行业资讯、最新开发方案等资讯信息平台。

Altera芯片今日搜索排行榜(2025年4月26日)

Altera产品及其应用

Altera公司新闻

买芯片网,独家代理渠道,专注三大品牌:XILINX(赛灵思 AMD)、ALTERA(英特尔 INTEL)、LATTICE(莱迪思)