观察两大可程式化逻辑元件供应商赛灵思(Xilinx)与Altera之间的较劲,就如同看苹果(Apple)与三星(Samsung)之间的战争一般令人兴奋;不过笔者并没有要比较上述两家公司,而是着重于他们尝试将技术推向极限以保持市场竞争优势的、令人屏息的热忱。

买芯片网专注整合全球优质Altera代理商现货资源,是国内领先的Altera(英特尔)、Lattice(莱迪思)、Xilinx(赛灵思 AMD)芯片采购服务平台,买芯片网轻松满足您的芯片采购需求.

Altera在不久前才发表了第十代Stratix系列产品(参考阅读:采用创新架构 Altera最新Stratix 10亮相);该公司所关注的设计挑战与今日的各种关键应用相关,包括资料中心、物联网(IoT)、400G/terabit网路、光学传输、5G无线通讯与8Kg讯。以资料中心为例,这类应用对更高的运算性能、灵活度与节能效益有越来越多需求;不过资料中心偏好使用商用伺服器,如此能更容易维护一个快速扩充的基础设施。

物联网是将各种智慧装置相互连结在一起,以及与云端或是资料中心连结;这类应用需要高频宽的基础设施,好将资料中心处理分析过的资讯传送到连网装置上。因此,Altera认为这类具备最高成长潜力的应用领域,将会同时带来为迎合以下需求必须克服的挑战:不断增加的功能、更高的频宽与灵活度,以及最基本的小尺寸与更低耗电需求;当然还有最低成本。

所有这一切无法轻易地在电路板上实现,理由与不断驱使我们实现更高整合度的原因是一样的:PCB的尺寸大到无法达成我们渴望的功能性。再加上互连介面的频宽限制,以及PCB走线的功率耗损,因此你有足够的动机持续追求摩尔定律(Moore‘s Law)的预测。

Altera以更精细的14纳米制程来因应以上挑战,而对手Xilinx则是在最新Virtex、Kintex 与Zynq系列产品采用台积电(TSMC)的16纳米制程(发表时间在Altera的Stratix 10问世前不久);不过因为有各种IP区块、嵌入式DRAM与快闪记忆体、影像感测器以及逻辑,成熟技术各自在不同的制程节点,积体(monolithic)解决方案已经不可行,所以两家公司纷纷采用异质3D封装技术。不过因为作法不同,在性能与成本方面也会有所不同。

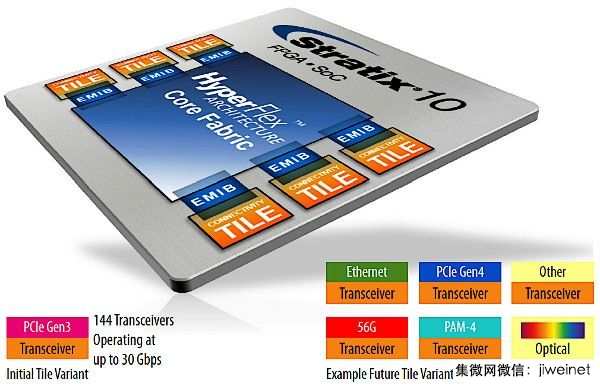

Altera的异质3D SiP技术将收发器裸晶(该公司称之为Tile)与核心FPGA结构裸晶分开,因此收发器是位于核心结构旁边,能以不同的制程节点来生产。

图1: Altera的异质3D SiP技术将收发器Tile与核心FPGA结构裸晶分开

因此能以不同的制程节点来生产

最初的Stratix 10收发器Tile,包括PCIe Gen3 x16硬IP区块;Altera表示,未来可能会推出其他硬体IP,例如PCIe Gen4、多埠乙太网路以及光收发器(更多Stratix 10相关资讯请参考此连结)。

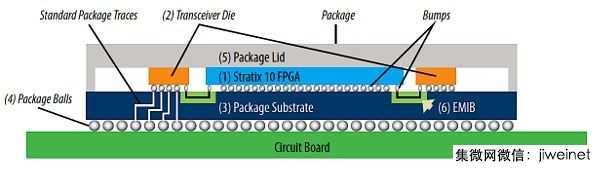

而Altera的解决方案与Xilinx产品最大的差异化,在于前者采用英特尔(Intel)专利的EMIB (Embedded Multi-die Interconnect Bridge)技术;EMIB是具备多绕线层(routing layer)的小型桥接晶片,可取代矽中介层(interposer)与矽穿孔(TSV)技术。

根据Intel与Altera的介绍,这种EMIB技术能降低讯号劣化与延迟的问题,因为裸晶不必透过中介层与TSV与封装连结。

EMIB vs. 矽中介层-TSV

在一般晶片封装中,矽中介层是一片比其他封装中的互连裸晶尺寸更大的矽;而EMIB这种矽桥接(bridge)则是一小片嵌入两片互连裸晶边缘之下的矽,这能让不同尺寸的裸晶在不同的地方连接,因此降低异质裸晶之间的物理限制

图2: EMIB技术能减少对微凸块的需求,因此降低制造的复杂度

在非EMIB解决方案中的大片矽中介层会(根据Altera说法是“过分地”)提高成本,而且容易出现像是变形曲翘的问题;EMIB也能降低对微凸块数量的需求──传统晶片会采用大量有微通孔的微凸块,这提升了制造复杂度也会影响良率,当然也是提高成本的因素之一。对于不太可能取得EMIB技术的竞争队史来说,Altera看来略胜一筹,不是吗?

Altera中国海量优质的信息资源、行业资讯、最新开发方案等资讯信息平台。