摘要:本文介绍了基于Xilinx Virtex-6 FPGA的高速串行数据传输系统的设计与实现,系统包含AXI DMA和GTX串行收发器,系统增加了流量控制机制来保证高速数据传输的可靠性。最后进行了仿真测试,测试结果显示系统可以高速可靠地传输数据。

买芯片网专注整合全球优质赛灵思代理商现货资源,是国内领先的Altera(英特尔)、Lattice(莱迪思)、Xilinx(赛灵思 AMD)芯片采购服务平台,买芯片网轻松满足您的芯片采购需求.

引言

随着数字多媒体技术的发展,在现代电子系统中各模块之间经常需要高速数据传输。传统的数据传输系统采用并行接口,并行数据传输技术向来都是提高数据传输速率的重要手段。随着数据传输速率的提高,并行数据传输的进一步发展遇到了瓶颈,面临很多问题,如接口信号不同步,信号串扰,引脚过多增加PCB板布线难度及设计制作成本。因此,高速串行接口已经逐渐取代并行接口。与并行传输相比,串行传输具有独特优势,可以提供更大的带宽更远的传输距离以及更低的成本。

高速数据传输系统中各模块规模以及复杂度逐渐加大,数据传输的可靠性逐渐成为影响系统性能的关键因素之一。数据发送模块和数据接收模块处理数据的速度很难达到一致,因此经常会出现接收模块等待发射模块发送数据,或者发送模块等待接收模块接受数据的情况。为了使高速数据传输系统可靠工作不丢失数据,系统需要加入流量控制机制,来协调发送模块和接受模块的工作。

系统结构

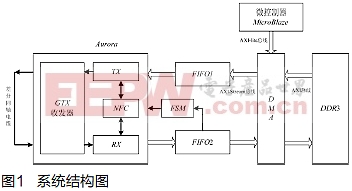

本系统基于Xilinx公司的Virtex-6系列的一款FPGA——XC6VLX240T,用于进行高速串行数据传输,其结构。系统主要包括微控制器MicroBlaze模块,直接存储器存取(DMA)模块以及基于Aurora协议以及GTX收发机的Aurora模块,另外还有内存模块(DDR3),两个作为缓冲器的FIFO模块以及一个用于流量控制的有限状态机(FSM)模块。系统的工作流程为:微控制器MicroBlaze通过AXI-Lite总线向DMA寄存器写数据,配置DMA读操作的数据源地址,读数据长度,DMA写操作的目标地址以及写数据长度,然后启动DMA。DMA开始读取DDR3源地址空间中的数据通过FIFO1传给Aurora模块,Aurora模块中的GTX收发器将数据通过同轴电缆以串行的方式从发射端发送到接收端。然后接收端将数据传输到FIFO2中,然后通过DMA将数据写入到DDR3内存规定的目标地址空间中。本系统中采用回路(loopback)的模式来方便地模拟串行数据传输系统。

以下分别对其主要模块进行介绍。

微控制器Microblaze模块

MicroBlaze是Xilinx公司推出的一款可以嵌入在FPGA中处理器软核,采用RISC架构和哈佛结构的32位指令和数据总线,具有丰富的适用于嵌入式应用的指令集,支持CoreConnect总线的标准外设集合,最新的MicroBlaze支持AXI总线。MicroBlaze运行速度快,占用资源少,具有很强的可配置性,在很多领域得到了广泛应用。

Xilinx中国海量优质的信息资源、行业资讯、最新开发方案等资讯信息平台。