在Xilinx的FPGA器件XC3S200-4FT200上对方案中设计的帧同步系统进行了实现,利用Modelsim 6.0软件进行了仿真测试。仿真结果表明,本方案设计的同步系统工作稳定,满足性能要求。

买芯片网专注整合全球优质赛灵思代理商现货资源,是国内领先的Altera(英特尔)、Lattice(莱迪思)、Xilinx(赛灵思 AMD)芯片采购服务平台,买芯片网轻松满足您的芯片采购需求.

0 引言

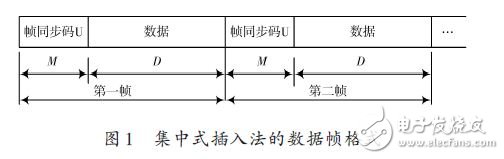

在数字通信系统中,发送端一般以一定数目的码元组成一个个“字”或“句”,即组成一个个数据帧进行 传输,因此帧是数据传输的基本单位。不同的通信系统具有不同的帧结构。帧一般分为帧同步码和数据两部分,帧同步码用于标志帧的起始位置;数据则是需要传输 的有效码元。帧同步码组的插入方法主要有两种:集中式插入法和间隔式插入法。集中式插入法就是在每帧的开头集中插入帧同步码组的方法;间隔式插入法则是将 帧同步码组分散插入到数据流中,即每隔一定数量的信息码元插入一个帧同步码元。本文主要提出一种集中式插入法帧同步的FPGA的设计方案。

一般来讲,帧同步在位同步之后才能进行。虽然信号的频率很容易由位同步信号经过分频得到,但是帧的起始和末尾时刻则无法由位同步信号分频确定。帧同步的主要任务就是要获取每个数据帧的起始及结束位置。随着可编程逻辑器件的发展,采用FPGA实现帧同步等数字系统具有速度快、使用方便、可编程配置各种参数等一系列优点,因而得到了越来越广泛的应用。

1 集中式插入法帧同步的原理及流程

1.1 集中式插入法帧总体结构

集中式插入法是指在每帧数据的开始位置集中插入帧同步码序列的方法。在这种同步传输方式中,被传输 的数据比特被编成帧,每帧包括多个数据,帧的首部加一个帧同步码组(也称为帧的标志字),记作U,其长度为M(单位:b),帧内的数据比特数为D.接收端 对接收的比特流进行搜索,一旦检测到标志字U,就知道了一帧数据的开始,并据此对帧内的数据进行分组处理,以此建立起同步传输机制。集中式插入法的数据帧 格式。

显然,帧同步码组必须满足一定的条件:首先,同步码组要求尽量与所要传输的数据不同,以免将数据误 认为是同步码组;其次要求帧同步码组具有尖锐单峰的自相关特性,以便于接收端进行正确检测;第三个要求是长度不能太长,以免占用过多的信道资源。目前常用 的帧同步码组主要有广义巴克(Barker)码序列,一些系统也使用具有伪随机特性的m序列作为同步码组。

1.2 帧同步的几种状态

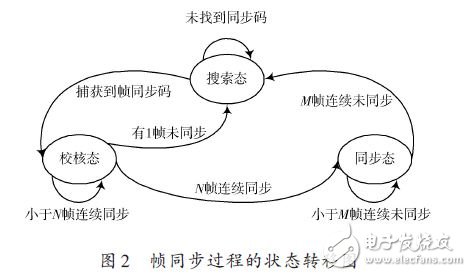

根据帧同步搜索的原理,在帧同步搜索过程中显然存在假锁的可能性(也称虚警概率),因为数据比特所 构成的码序列,或部分的标志字与部分的数据比特所构成的长度为M 的码序列也有可能满足检测条件,而被误认为U.因此,为了提高帧同步系统的性能(减小假锁的概率,锁定后尽量增加同步的稳定性),工程上通常通过增加同步 流程的复杂性来实现改善性能的目的。一般来讲,将帧同步的过程分为三个状态:搜索态、校核态和同步态,其状态转移图。

搜索态:在数据接收的起始时刻,或帧校核时出现未同步帧,或同步态时发现有多个连续帧未同步时转入搜索态。搜索态下,程序在数据流中持续搜索帧同步码,当从接收到的比特流中找到帧同步码时,表明已搜索到了一个同步帧头,此时输出一个脉冲信号,系统可进入校核态。

校核态:若连续经过N 帧同步码确认搜索态中找到的帧头正确,则系统可立即转入同步状态;否则说明存在假同步,需要返回搜索态重新对帧同步码进行搜索。由首次搜索到帧同步头到进入同步态的N 帧时间叫做后方保护时间。

同步态:帧同步系统处于同步状态时,若没有出现连续M 帧数据未同步,则保持在同步状态。考虑到接收的数据流中可能受外界干扰而存在误码,在同步状态中只有连续M 帧丢失同步码才进入失步状态,并返回搜索态,这个M 帧的时间叫做前方保护时间。

Xilinx中国海量优质的信息资源、行业资讯、最新开发方案等资讯信息平台。