摘要:针对雷达现场中复杂多变的电磁信号难以及时分析处理,本文提出了一种基于高速串行接口的雷达中频信号采集回放系统。该系统充分利用JESD204B高速串行接口和吉比特收发器,通过Xilinx Virtex FPGA芯片对其进行控制,实现雷达中频信号的高速、高精度、可靠、稳定采集和回放,有效地解决了高速数据流并行传输时存在码间串扰的问题。

买芯片网专注整合全球优质赛灵思代理商现货资源,是国内领先的Altera(英特尔)、Lattice(莱迪思)、Xilinx(赛灵思 AMD)芯片采购服务平台,买芯片网轻松满足您的芯片采购需求.

背景

雷达现场环境中的电磁信号不仅包含了目标信息,还包含了电子干扰、天气、地形等丰富的信息,其信号数量庞大和信号种类多样的特点致使后期难以及时实现高速数据流的处理和分析。因此,如何实现雷达现场信号的高速采集和重现是现今讨论尤为激烈的话题之一。同时,这对雷达外场试验、演习数据分析、雷达检修和部队训练都有着重要的现实意义。

在现代雷达信号处理系统的研制中,一般需要对中频雷达信号进行高速度和高精度采集。目前使用的并行采样传输模式虽然可以实现此要求,但是随着采集速率的提高,并行数据之间的误码率也在成倍增加[1]。本文采用带有高速串行接口JESD204B的模数转换芯片实现多路雷达中频信号的高速度、高精度采集,以Xilinx Virtex-6配备的多路吉比特收发器进行采集数据流的可靠稳定传输,并使用可进行4倍插值的数模转换芯片实现高速信号的高精度模拟转换。FPGA作为该系统的主控,不仅完成了各器件的配置,而且实现了采集和回放过程的数据信道化,使得系统更完整,通用性更强。

1 系统框图

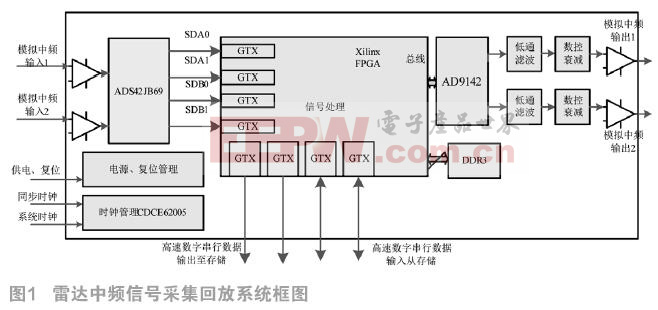

该雷达中频采集回放系统设计。该系统主要包括四个模块:A/D模块、D/A模块、信号处理模块和时钟复位管理模块。ADC模块主要是通过ADS42JB69实现双通道16位250MSPS高速采样,其前端可由两路放大器及变压器对中频模拟信号进行调理,使之符合ADC芯片射频输入端口的要求;DAC模块主要由AD9142芯片、低通滤波器、数控衰减器和放大器组成,通过对DAC芯片进行4倍插值可以实现16位高达1000MSPS的数模转换;信号处理采用XC6VLX240TFF1156芯片对各模块进行管理并实现数据的信道化处理;时钟复位管理模块包括图1中所示的电源、复位管理和时钟管理,其主要功能是为系统中的其它模块提供供电、时钟和复位等。

2 高速串行接口

2.1 JESD204B

JESD204B 协议体系结构可分为物理层、链路层、传输层和应用层。物理层实现高速数据串/并行转换、并/串行转换以及编码处理;链路层负责编码帧数据、校验数据、添加帧的边界和流量控制,过程中只发送和接收帧而无需知道帧的内容[2];传输层则是将AD采样信息从数据流中提取出来。JESD204B接口由接收器和电流模式逻辑(CML)驱动器的差分对组成,共模拟电平范围为0.72V~1.23V,通信速率可低至312.5Mbps,可高达3.125Gbps[3]。相比于其它接口,它不仅实现了高速数据的可靠稳定传输,而且在硬件上减少了管脚数量,简化了ADC和FPGA的布线,特别是对于多片ADC的系统。JESD204B接口的这一特性使其拥有广阔的应用前景。

2.2 GTX

Virtex-6 FPGA是Xilinx公司推出的一块高性能低功耗FPGA[3]芯片。本文选用XC6VLX240TFF1156芯片,该芯片内嵌5个Quard,每个Quard包含4个千兆位收发器GTX,每个GTX收发器都集成了发射器和接收器功能,能以480MB/s~6.6GB/s的速率运行,且其有大量可配置的用户定义特性和参数[4]。其结构由物理媒介适配层PMA(Physical Media Access)和物理编码子层PCS(Physial Code Subplayer)两部分组成。PCS提供丰富的物理编码层特性,包括周期冗余检测CRC(Cyclic Redundancy Check)、8B/10B编码、发送FIFO、8B/10B解码及用于通道绑定和时钟校准的弹性缓冲器等模块;PMA部分为模拟电路,提供高性能的串行接口特性,如预加重和均衡等功能,主要包括串行转换、差分接收器、并串转换及时钟数据恢复(CDR)等模块[5]。

对于GTX的时钟可以选择外部供给,而且相邻的Quard可以使用同一对差分时钟。发送端用户时钟TXUSRCLK2是由TXOUTCLK驱动,接收端用户时钟RXUSRCLK2是由RXRECCLK驱动,即是从接收到的数据里恢复出来的时钟[6]。要注意发送端还有另外一个用户时钟TXUSRCLK是PCS内部逻辑时钟,不允许用户直接使用,接受端的RXUSRCLK类似,其速率为线速率与数据位宽之比。

GTX接口众多特性使其能够方便地实现PCIE、SATA、SAS等高速串行接口的物理层与链路层桥接。本文使用GTX接口实现JESD204B协议,以正确解析JESD204B接口ADC转化器发出的数据。

3 信号处理

3.1 A/D

基于JESD204B标准设备与FPGA内嵌的吉比特收发器可实现完美对接,该系统选用TI公司生产的ADS42JB69作为A/D转换的主要器件。它是一款高线性、双通道、16位、250MSPS的模数转换器,支持JESD204B串口,数据速率高达3.125Gbps。经缓冲的模拟输入在大大降低采样保持毛刺脉冲能量的同时,在宽频率范围内提供统一的输入阻抗,这使得它可以轻松地将模拟输入驱动至极高输入频率[7]。采样时钟分频器可实现更灵活的系统时钟架构设计。此期间采用内部抖动算法以在宽输入频率范围内提供出色的无杂散动态范围(SFDR)。

ADS42JB69首先根据需要完成数据采集,然后通过JESD204B接口将采集的并行数据送至FPGA。根据模数转换的最大速率,JESD204B可配置成两种工作模式:四线模式和两线模式。本文假定ADC的采样速率为250MSPS,那么JESD204B接口就必须工作在四线模式,即DA0和DA1分别对应A通道的高低8位,B通道同理。其中, 端口用来控制串行端口输出的数据类型,其可作为多片ADC采集的同步控制。此外,还可通过SPI对ADC芯片的寄存器0x0f进行配置,实现除了正常工作模式外的多种测试模式,如递增码、随机码、零一交错码等。JESD204B完成数据传输要经过两步:编码以及串并转换。本文使用8B/10B编码,结合A/D转换速率,发送端的线速率就是;如果采用双通道进行采集,那么总的数据量就是。

在串行数据收发过程中如何界定数据的边界是至关重要的。JESD204B协议采用插入控制字符以完成字同步和帧同步来确定数据的边界,结合接收端对端口的控制,可实现采集数据的准确和可靠传输。本文对其控制实现可分为三步:

第一步:接收端拉低,发送端持续发送/K28.5/ 控制字。当接收端接收到4个/K28.5/字符后表明字同步建立完成,此时,接收端也已经完成时钟恢复以及Comma字符坚持测;

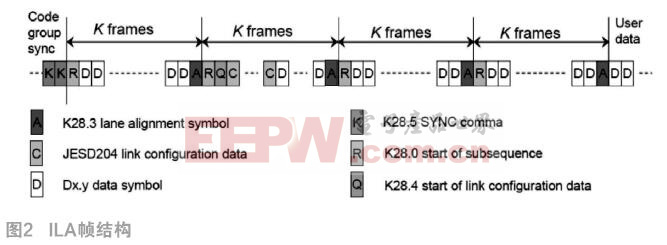

第二步:接收端拉高,发送端开始发送ILA帧。每个ILA包含4个多帧(Multi-Frame)。帧的结构;

第三步:当接收端接收到ILA帧后就表明采集数据开始,其中可通过判断/K28.3/字符的个数来确定起始有效数据。

3.2 D/A

进行数模转换的关键是器件的选择以及配置。本文选择ADI公司生产的AD9142作为本系统的数模转换芯片。AD9142是一款双通道、16位、高动态范围的数模转换器,可通过插值实现最高1600MSPS的采样速率,并可产生高达奈奎斯特频率的多载波。它具有针对直接变频传输应用进行优化的特性,其中包括复数数字调制、输入信号功率检测以及增益、相位与失调补偿。3线式串行接口允许对内部寄存器进行编写和回读,是一款高性能、低噪声的数模转换芯片[8]。

如果要实现采集信号的实时回放,那么数据时钟(DCI时钟)就是250MSPS,SPI总线配置AD9142完成4倍插值就可实现高达1000MSPS的数模转换。为确保AD9142实现可靠及高性能工作,其必须遵循一定的步骤,具体为(从器件上电后开始):

第一步:时钟芯片CDCE62005提供稳定的数模转换DAC时钟,项目中配置为1000MHz;

第二步:FPGA提供稳定的数据同步DCI时钟,项目中FPGA提供250MHz LVDS电平的差分时钟;

第三步:SPI总线发出复位命令复位芯片,并配置其它相关参数,如PLL、数据接口、插值滤波器、NCO、SINC等;

第四步:SPI总线配置完成后,提供稳定的数据实现数模转换。

3.3 信道化

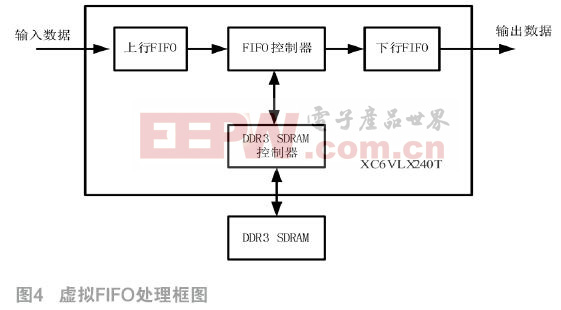

对于雷达中频采集回放系统,为了满足后端存储速率不定的要求,本文设计了基于FPGA的信道化处理框图,增强了系统的通用性。

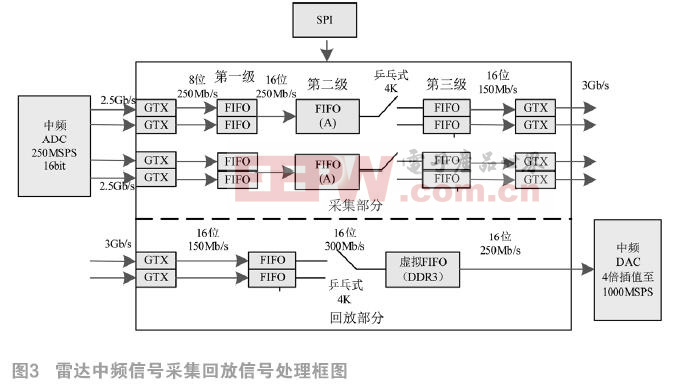

,对于采集部分,因为每路ADC都是以高低字节分开的方式传输数据,因此要严格保证采样时钟同步,这在工程中很难实现。第一级FIFO设置存储深度为32B,当FIFO中可读数据达10个后,开始以同一个时钟读取FIFO,完成采样数据高低字节的同步以及拼接;第二级FIFO作为数据缓存,深度设置为8KB,不仅杜绝了前端拼接后数据出现亚稳定状态,而且为后续用户逻辑提供简单接口[9]。当FIFO可读数据达到4KB时,READY信号拉高,开始向第三级FIFO写入数据;第三级FIFO除了作为乒乓式读取上一级FIFO的缓存,还为后续GTX编码争取更多时间。三级FIFO联合工作可实现告诉采集数据流的可靠稳定传输[10]。

本文来源于中国科技期刊《买芯片网》2016年第5期第73页,欢迎您写论文时引用,并注明出处。