简介

买芯片网专注整合全球优质赛灵思代理商现货资源,是国内领先的Altera(英特尔)、Lattice(莱迪思)、Xilinx(赛灵思 AMD)芯片采购服务平台,买芯片网轻松满足您的芯片采购需求.

JESD204是一种连接数据转换器(ADC和DAC)和逻辑器件的高速串行接口,该标准的 B 修订版支持高达 12.5 Gbps串行数据速率,并可确保 JESD204 链路具有可重复的确定性延迟。随着转换器的速度和分辨率不断提升,JESD204B接口在ADI高速转换器和集成RF收发器中也变得更为常见。此外,FPGA和ASIC中灵活的串行器/解串器(SERDES)设计正逐步取代连接转换器的传统并行LVDS/CMOS接口,并用来实现 JESD204B物理层。本文介绍如何快速在Xilinx® FPGA上实现JESD204B接口,并为FPGA设计人员提供部分应用和调试建议。

JESD204B 协议实现概述

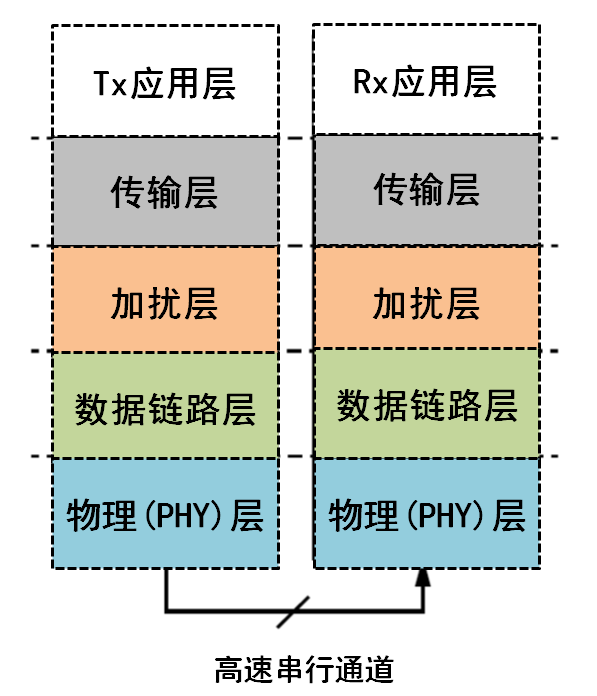

JESD204B规范定义了实现该协议数据流的四个关键层,。传输层完成样本和未加扰的帧数据之间的映射和解映射。可选的加扰层可用来加扰/解扰8 位字,以扩散频谱尖峰来降低EMI。数据链路层处理链路的同步、建立与保持,并对加扰后的数据进行8B10B编码或译码。物理层负责以比特速率发送和接收编码后的字符。

图1. JESD204B标准的关键层级

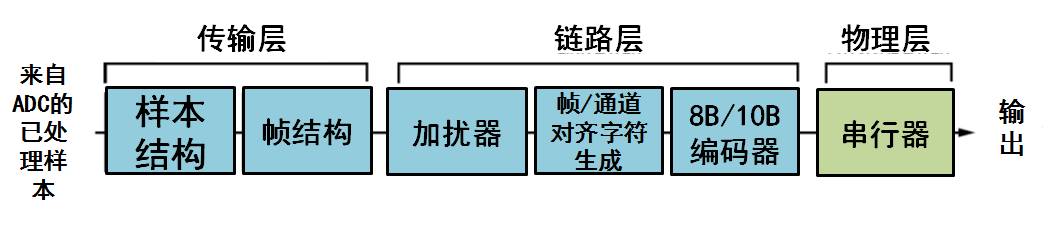

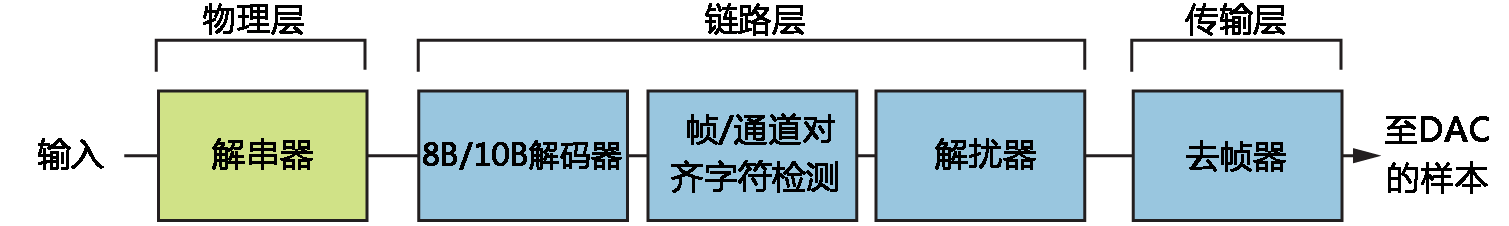

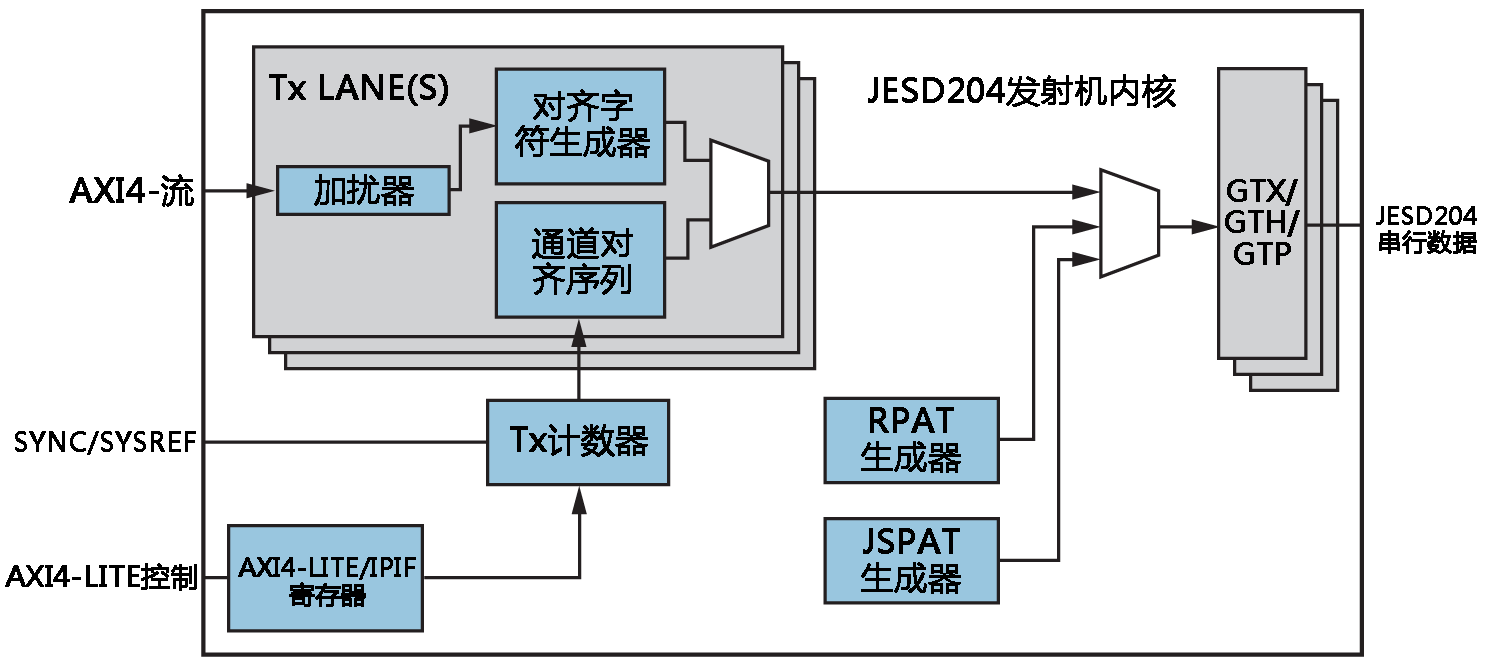

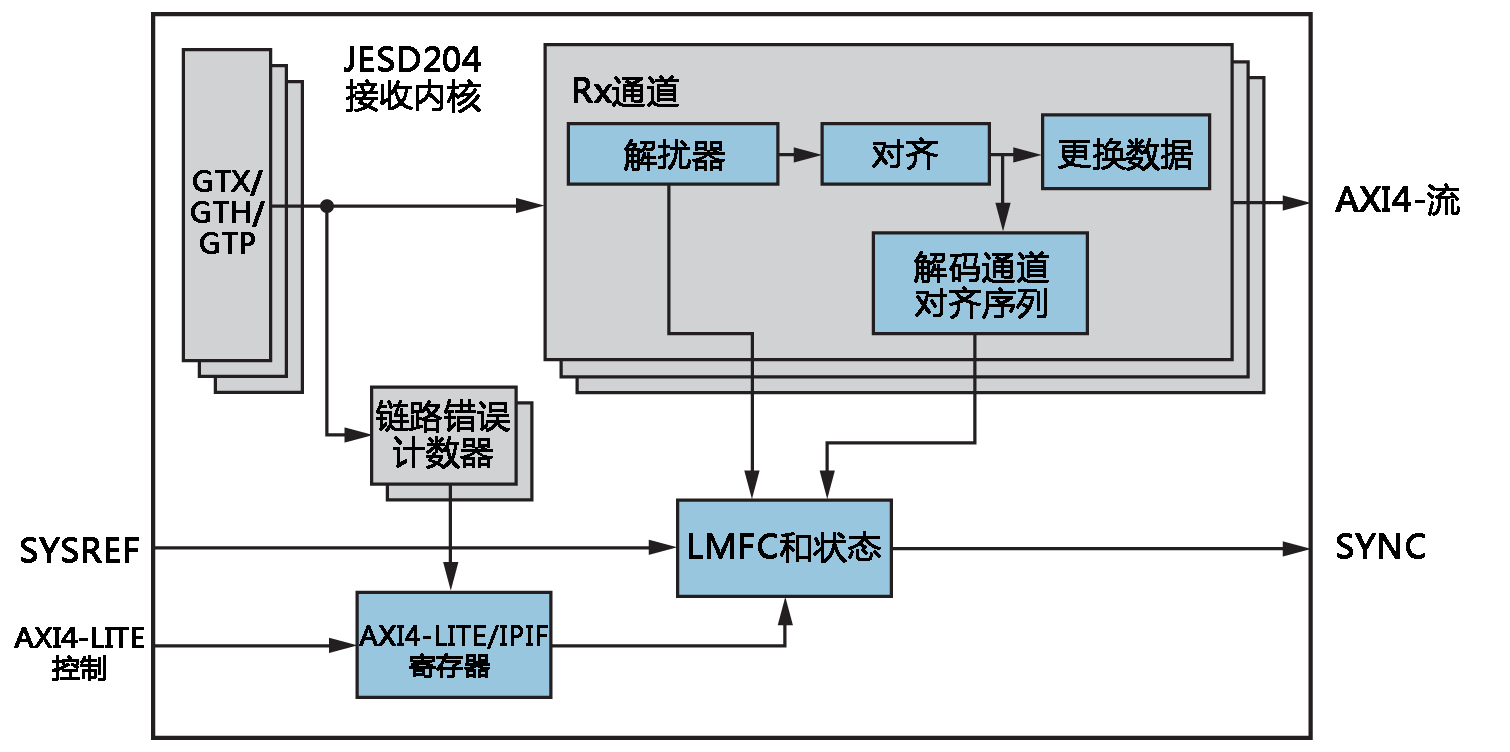

不同的JESD204B IP供应商可能以不同的方式实现这些层级。图 2和图3显示ADI如何实现JESD204B的发送和接收协议。

图2. JESD204B发送器实现

图3. JESD204B接收器实现

传输层实现和特定的转换器配置及其样本与帧之间的映射方式强相关,因此大部分FPGA供应商将其排除在各自的JESD204 IP之外。此外,FPGA集成了高度可配置、高集成度的SERDES收发器,这些SERDES收发器可用来支持所有类型的串行协议,包括PCIe、SATA、SRIO、CPRI和JESD204B。因此,一个实现链路层的逻辑核和实现物理层的可配置SERDES 便构成了JESD204B 链路的基础。图4 和图5 显示Xilinx FPGA上的JESD204B发送器和接收器框图。发送器/接收器通道实现加扰和链路层;8B/10B 编码器/解码器和物理层在 GTP/GTX/GTH Gbit 收发器中实现。

图4. 使用Xilinx FPGA实现JESD204B发送器

图5. 使用Xilinx FPGA实现JESD204B接收器

采用Xilinx FPGA的JESD204B设计示例

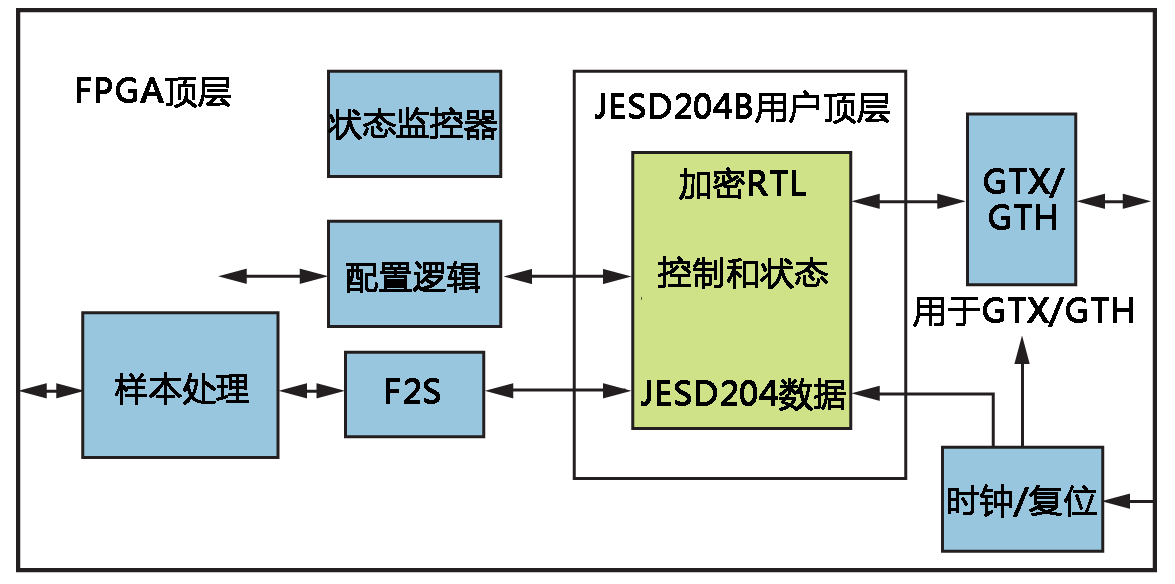

最新的 Xilinx JESD204 IP 核通过 Vivado®设计套件以黑盒子加密交付。Xilinx还提供使用高级 eXtensible接口(AXI)的Verilog设计示例,但该示例项目对大部分应用而言是过设计的, 因为用户通常采用自己的配置接口,无需针对JESD204B 逻辑集成一个额外的AXI。图6 显示的是一个JESD204简化设计,旨在帮助FPGA用户理解JESD204结构,并让他们快速着手设计自己的JESD204 FPGA项目。

图6. JESD204B设计示例

Vivado产生的JESD204逻辑IP核,即经过加密的 RTL 摸块相当于图4和图5中的发送和接收模块,其加密接口定义可在Xilinx示例设计文件中找到。然后,可将经过加密的RTL 模块嵌套入JESD204B用户顶层。来自加密RTL 模块的控制、配置、状态和JESD 数据接口直接通过嵌套层连接到用户逻辑和GTX/GTH收发器。GTX/GTH符号对齐配置经优化和更新,使收发器工作更为稳定。

给SERDES收发器的GTX/GTH参考时钟应采用专用引脚,对用于FPGA逻辑的全局时钟设计必须仔细的考虑,包括内部PLL、并行接口时钟、JESD204逻辑核以及用户逻辑时钟。此外,必须 确保给JESD204B逻辑核(子类1)的SYSREF输入被准确采到,以确保JESD204链路的确定性延迟。

若要获得可靠的JESD链路初始化性能,GTX/GTH收发器和JESD204核的复位序列十分关键;因此,JESD204核应处于复位状态,直到GTX/GTH收发器的内部PLL 锁定,且GTX/GTH复位完成。

F2S 模块实现JESD204的传输层,该模块根据特定JESD204B配置将样本映射至帧,或从帧解映射至样本。然后根据特定的应用去处理样本数据。采用辅助模块监测JESD204逻辑和物理层(PHY)状态,供系统调试。/p>

Xilinx SERDES收发器的符号对齐

在SERDES接收器中,串行数据必须与符号边界对齐,才能用作 并行数据。为了对齐数据,可让发送器发送一个可供识别的序 列,通常称为"逗号"。接收器搜索输入串行数据流中的逗号, 一旦找到便将其移到符号边界。这样可让接收到的并行字与发 送的并行字相匹配。逗号通常用K 码表示,它是8B/10B表中用 作控制符的一些特殊字符。对于JESD204B应用,发送器发送K = K28.5符号流,以便进行码组同步(CGS)。因此,FPGA可采用 K28.5 作为逗号,来对齐符号边界,而用户可以指定逗号匹配是 由极性为正的逗号或是由极性为负的逗号所组成,或由两者共同 组成。JESD204B针对GTX/GTH逗号检测的默认设置允许利用 正极性逗号或负极性逗号来对齐。

某些应用中,默认逗号设置可能导致符号的重新对齐,或者对齐至错误的符号边界。这可能会导致大量的8B/10B解码错误,并使JESD204B链路断链。而正极性逗号加上负极性逗号使用会更稳定,可以使逗号对齐模块连续搜索两个逗号,并仅当收到的数据为正极性逗号(或负极性)后跟一个负极性逗号(或正极性逗号)且中间无额外位时才认为检测到逗号。当线路速率较高或系统噪声过多时,这样做有助于保持符号边界和链路稳定性。

FPGA上的JESD204项目设计考虑因素

来自JESD204 接收器输出到发送器的同步、低电平有效SYNC信号用于表示同步状态。正常工作时,链路重新初始化将导致样本数据混乱,因此必须实时监测链路状态。具体而言,SYNC上的连续低电平表示接收器在接收到的数据流中无法识别出至少四个连续K28.5符号。如果发生这种情况,请检查发送器/接收器SERDES 配置,或确保发送器正在发送K28.5。SYNC上的连续高电平表示链路已建立,且保持稳定。若SYNC从高电平变为低电平然后返回高电平,则必须记录低电平状态的持续时间。如果持续时间长于5个帧加9 个字节,则表示接收器检测到了较大的错误,并将发送请求以重新初始化JESD204链路。如果持续时间等于两个帧时钟,则表示接收器检测到了较小的错误,但不会触发链路重新初始化。这个功能可极大地简化系统调试,并为进一步的链路监测提供便利。因此,用户应当在设计中包含这个功能。

8B/10B解码错误可能导致JESD204B链路重新初始化,但这并非是唯一的原因;因此,用户在设计时应能够对各通道的解码错误进行计数,从而确定链路重新同步的原因。此外,可通过8B/10B解码错误状态实时确定SERDES链路质量。

伪随机位序列(PRBS)提供了一个测量高速链路中信号质量和抖动容差的有用资源。大部分FPGA 中的SERDES收发器都内置了PRBS发生器和检查器,无需额外的FPGA资源。因此,不要忘了实例化此功能,在评估比特误码率(BER)或眼图时会使用到这个功能。

SERDES收发器中通常会使用一个缓冲器,来改变内部时钟域。如果发送器和接收器的时钟设计不佳或者时钟数据恢复模块(CDR)设置错误,那么就会导致缓冲器上溢或下溢。此时可能会发生某些链路错误,因此有必要监测缓冲器状态。缓冲器上溢或下溢的中断记录对于系统调试而言是很有用的,所以同样应当监测用户逻辑中不允许发生下溢或上溢的其它内部缓冲器的状态。

结论

本文讨论了如何在Xilinx FPGA上快速实现JESD204模块,实现方法同样可用于其它FPGA。首先,应了解FPGA供应商提供的JESD204逻辑核和收发器的功能以及接口,然后将其实例化并与您的逻辑整合。其次,从全局角度出发设计FPGA时钟树,和整个工程的复位顺序。然后,仔细定义JESD204逻辑核、用户逻辑和收发器之间的接口。最后,加入必要的调试资源。遵循这些步骤有助于您快速、成功地设计JESD204接口。

Xilinx中国海量优质的信息资源、行业资讯、最新开发方案等资讯信息平台。