在数字信号处理领域,如自适应滤波、DPD系数计算、MIMO Decoder 等,常常需要矩阵解方程运算以获得其系数,因此需对矩阵进行求逆运算。然而,由于直接对矩阵求逆会导致庞大的运算量,所以在实际工程中往往需要先将矩阵分解成几个特殊矩阵(正规正交矩阵或上、下三角矩阵以求其逆矩阵需要更小的运算量)的乘积。目前,QRD矩阵分解法是求一般矩阵全部特征值的最有效且广泛应用的方法之一。它是将矩阵分解成一个正规正交矩阵Q与上三角形矩阵R,称为QRD矩阵分解。

买芯片网专注整合全球优质赛灵思代理商现货资源,是国内领先的Altera(英特尔)、Lattice(莱迪思)、Xilinx(赛灵思 AMD)芯片采购服务平台,买芯片网轻松满足您的芯片采购需求.

由于浮点具有更大的数据动态范围,所以在众多多算法中具有只需要一种数据类型的优势,所以很多QRD矩阵分解是基于浮点数据类型的。不过在通信应用中,更多的场景还是复数类型。因此,随着通信技术的日益发展,算法的复杂度越来越高,QRD矩阵的维度也越来越大。如果是用传统的手写RTL,浮点复数超大维度QRD矩阵分解的FPGA实现将变得非常复杂,需要很长的时间来编写RTL代码、仿真和进行验证等工作,使得开发效率不是很高。

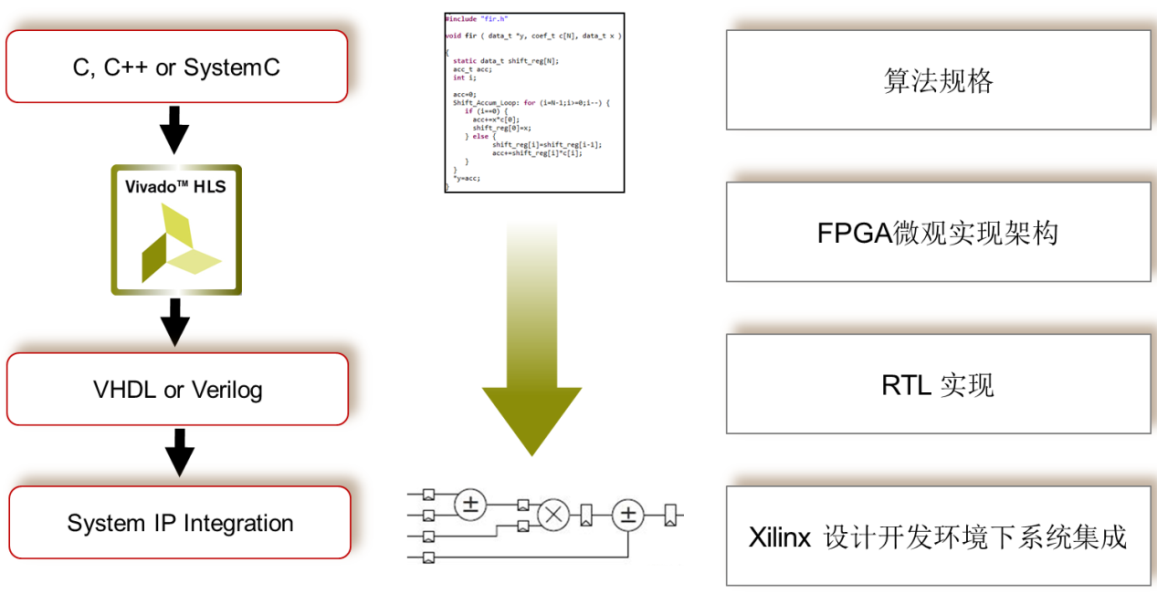

本文将介绍如何使用Xilinx Vivado HLS(Vivado 高层次综合)工具实现浮点复数QRD矩阵分解并提升开发效率。使用Vivado HLS可以快速、高效地基于FPGA实现各种矩阵分解算法,降低开发者对算法FPGA的实现难度。其中包括:

使用Vivado HLS开发效率比手写RTL实现快5-10倍,而实现的FPGA资源效率与手写RTL接近 由于C/C++仿真验证比传统FPGA RTL要快100倍,Vivado HLS实现可以大大缩短用户的代码开发时间和仿真验证时间,从而大幅提高生产效率。1. Vivado HLS工具介绍

Vivado HLS 是Xilinx公司2010 年收购 AutoESL 以后重新打造的高层次综合工具,它可以让用户通过添加适当的directives(制导语句) 和 constrains(约束), 将其C/C++/System C代码直接转换成 FPGA RTL( Verilog, VHDL, System C )代码。让用户可以在算法开发环境而非通常的硬件开发环境中只需专注于算法规格和算法的 C 实现,Vivado HLS 工具会自动考虑 FPGA 微观实现架构,并可生成可综合的FPGA RTL代码。。

图1 Vivado HLS设计介绍

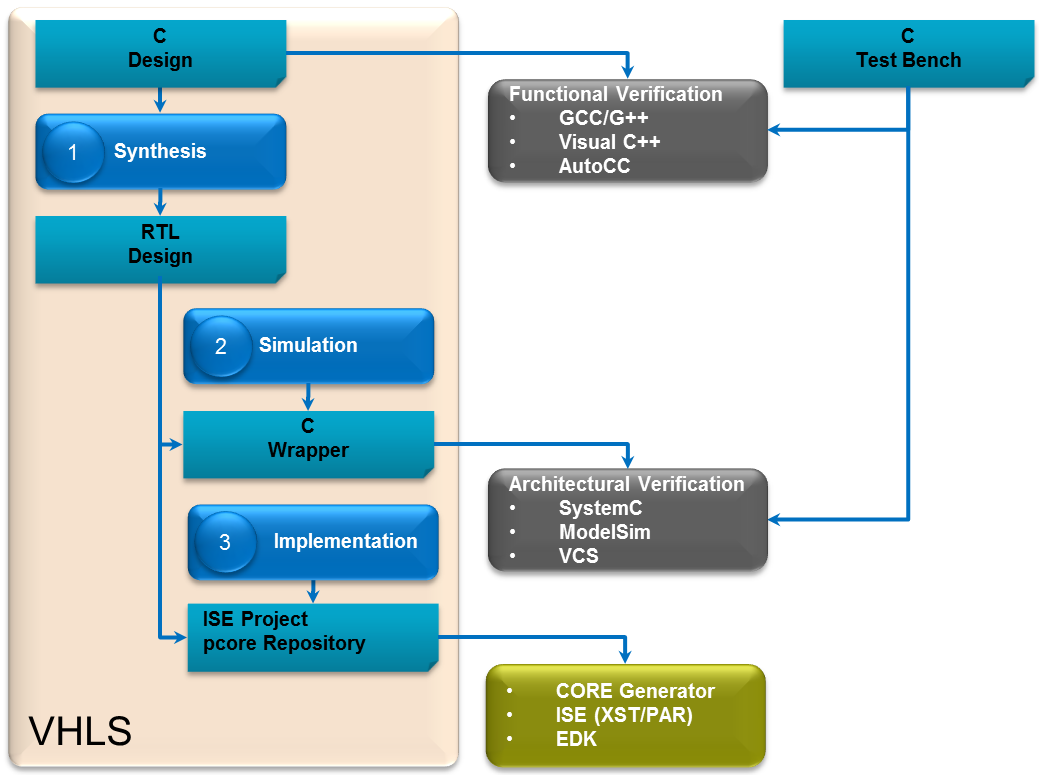

Vivado HLS FPGA设计流程:

首先用 C/C++/System C 将算法实现,并编写 C testbench 验证 C 的功能,确保其功能正确; 然后就可以通过 Vivado HLS 工具进行 C 综合,将 C 转换成 RTL; 接着做 C/RTL 的协同仿真(Co-simulation),以保证生成的RTL代码功能与C的功能完全一致。 最后 Vivado HLS 生成的 RTL 代码可直接用于 Xilinx 设计开发环境下做系统集成、仿真和生成bit文件。

图2 Vivado HLS设计流程

2. QRD矩阵分解算法

QRD矩阵分解是将一个矩阵A分解成Q与R相乘,

其中R是个上三角矩阵, Q是个正交矩阵,

Q = 1

是Q的转置共轭矩阵

3. QRD矩阵分解 Vivado HLS 实现C++代码构架

QRD矩阵分解C++实现代码的顶层模块是qrd_engine.cpp, 它调用cal_core.cpp(核心计算函数), coef_cal.cpp(系数计算函数),以及浮点加、减、乘、除法等子函数来实现。

struct cf_t {

float re;

float im;

};

void qrd_engine

(

cf_t in_u[(R_DIM+Y_DIM)/DIV_NUM][DIV_NUM],

cf_t pd_err_in,

float lamda,

float lamda_sqrt,

float diag[R_DIM],

cf_t r[R_DIM][X_DIM],

cf_t p[R_DIM]

)

{

#pragma HLS ARRAY_PARTITION variable=in_u complete dim=2

#pragma HLS ARRAY_PARTITION variable=r complete dim=2

//注:这里对数组加入完全分割directive,目的是提高数据的并行带宽,从而获得并行计算。

#pragma HLS RESOURCE variable=in_u core=RAM3S

//注:这里对数组加入RAM3S directive,目的是控制生成的BRAM的延迟。

for (i=0;i

{

#pragma HLS PIPELINE II =124

#pragma HLS latency max = 123

//注:这里加入II(interval是指下一个新的可以输入QRD模块的数据与前一个数据之间所间隔的时钟周期数)及latency directives (延迟制导语句),目的是控制这个模块在指定的延迟节拍范围内完成所有的计算。

coef_calc(lamda_sqrt,lamda,diag[i],pre_in_u,pd_err_in,&s_o,&s_conj_o,&lamda_sqrtxs_o,&c_o,&lamda_sqrtxc_o,&diag_out,&p_o,&pd_err);

cal_core(u_tmp, r_tmp, s_n, i, j, k, c_o, lamda_sqrtxc_o, lamda_sqrtxs_o, s_conj_o, &in_u_w2, &r[i][r_addr]);

}

}

void coef_calc

(

float lamda_sqrt,

float lamda,

float r_diag,

cf_t u_diag,

cf_t pd_err_in,

cf_t *s,

cf_t *s_conj,

cf_t *lamda_sqrtxs,

float *c,

float *lamda_sqrtxc,

float *diag,

cf_t *p_o,

cf_t *pd_err

)

void calc_core

(

cf_t in_u,

cf_t r,

int s_n,

int i,

unsigned char j,

unsigned char k,

float c_o,

float lamda_sqrtxc_o,

cf_t lamda_sqrtxs_o,

cf_t s_conj_o,

cf_t* u_ret,

cf_t* r_ret

)

4. QRD矩阵分解的Vivado HLS设计实现与优化

4.1 C模块划分

Vivado HLS生成的RTL代码在默认情况下保留原有c代码的层次结构。在构建c代码层次时,可以采用由上至下、自下而上相结合的模块划分方式。

将单精度浮点基本运算如加、减、乘、除、平方根等写成最底层的子函数,以便添加directives来指导工具优化方向。

float hfmult

(

float in1,

float in2

)

{

#pragma HLS PIPELINE

// 注:将hfmult函数流水化设计,以获得更好的时序性能

#pragma HLS RESOURCE variable=return core=FMul_fulldsp latency=9

// 注:制定hfmult的延迟为9个时钟周期,以便hfmult内部实现有充分的时钟节拍流水,特别是有足够的时钟节拍分配给DSP48内部做流水处理

float out;

out = in1 * in2;

}

类似的设计方法及思路也同样适用于浮点加,减等运算。

4.2 提高C转换成FPGA RTL 实现的并行度

由于计算时间、速度的要求,往往需要提高运算的并行度,需要对qrd_engine中in_u及r数组(HLS综合成FPGA的BRAM或分布式RAM)加数组分割directive,这样数据才可以并行进入后面的并行处理单元。

#pragma HLS ARRAY_PARTITION variable=in_u complete dim=2

#pragma HLS ARRAY_PARTITION variable=r complete dim=2

4.3 对数组memory地址读写设计优化

C语言中的数组通常会被综合成FPGA的存储memory,这样就会有地址的读写。但为了达到更好的时序性能,可以尽量减少对memory的读写,从而简化所生成RTL代码中的mux。

写法1,定义成,in_u[i/DIV_UNM][i%DIV_NUM],对下面的运算,将产生两次memory读写。

calc_coef(lamda_sqrt, in_u[i/DIV_UNM][i%DIV_NUM], …);

for(j=0; j

for(k=0; k

{

in_u_read = in_u[u_addr][k];

}

写法2,定义成变量in_u_pre, 通过 if(u_addr == (i+1)/DIV_NUM && k==(i+1)%DIV_NUM)判断来实现同样的功能,这样只需要一次memory读写,从而获得更好的II性能,当然也提升了时序性能。

calc_coef(lamda_sqrt, in_u_pre, …);

for(j=0; j

for(k=0; k

{

in_u_read = in_u[u_addr][k];

if(u_addr == (i+1)/DIV_NUM && ==(i+1)%DIV_NUM)

in_u_pre = in_u_read;

}

有时为了使in_u综合出的RAM时序更好,也可以对in_u综合的RAM加resource directive来控制其stage, 比如为3 stage,这样生成的RAM, 在输入,输出都会打一拍register。

#pragma HLS RESOURCE variable=in_u core=RAM3S

4.4 浮点运算加法级联与加法树

由于浮点运算的精度与其运算的先后顺序有直接关系,在Vivado HLS中,为了保证生成的RTL代码与C中的精度一样, Viado-HLS一般不会改变代码中中浮点运算的顺序。有时为降低浮点运算的latency,使用并行加法树将比串行级联加法来获得更有效。

浮点串行加法级联,这样写法是有严格先后顺序的,Vivado HLS将其生成串行实现的RTL代码,其latency为35个时钟周期。

void fp_adder_cascade (float *r, float a, float b, float c, float d)

{

#pragma HLS PIPELINE

*r = a + b + c + d;

}

如果用户确定上面的浮点加顺序调整对精度的影响在误差范围内, 那么可以采用并行加法树,这样 Vivado HLS 将其生成并行加法RTL代码实现,其latency为降为23个时钟周期。

void fp_adder_tree (float *r, float a, float b, float c, float d)

{

#pragma HLS PIPELINE

float e, f;

e = a + b;

f = c + d;

*r = e + f;

}

4.5 对浮点乘法使用的DSP48的优化

同样我们也可以通过设置充足的latency directive给DSP48,这样有足够的时钟节拍给到DSP48内部打拍register。

如果对上述的单精度浮点乘法hfmult latency设置为3,这样分配到每个DSP48 内部只有2级latency, 那么综合总合出来代码DSP48内部的A_reg 或 P_reg不会打一拍, 这样将会大大降低时序性能。

derive_core fmul_der -base FMul_maxdsp -latency 3 -fixed

set_directive_resource -core fmul_der hfmult out

或者:

为了达到较好的时序性能,对上述的单精度浮点乘法hfmult latency至少设置为4,这样分配到每个DSP48 内部只有3级latency, 那么综合总合出来代码DSP48内部的A_reg 或 P_reg都会各打一拍。

derive_core fmul_der -base FMul_maxdsp -latency 4 -fixed

set_directive_resource -core fmul_der hfmult out

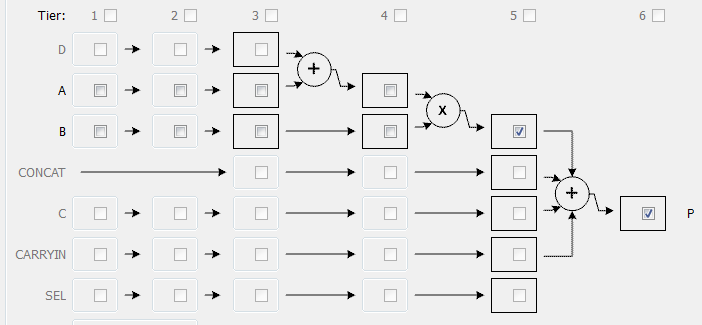

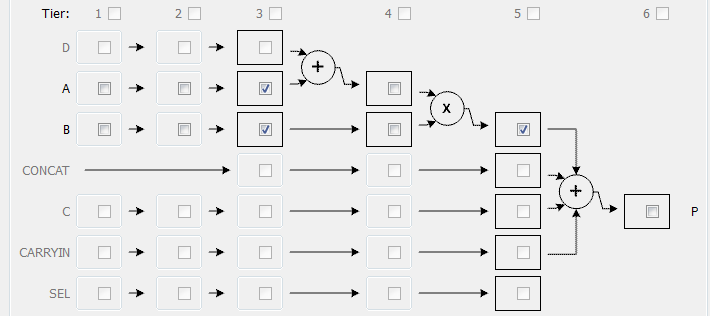

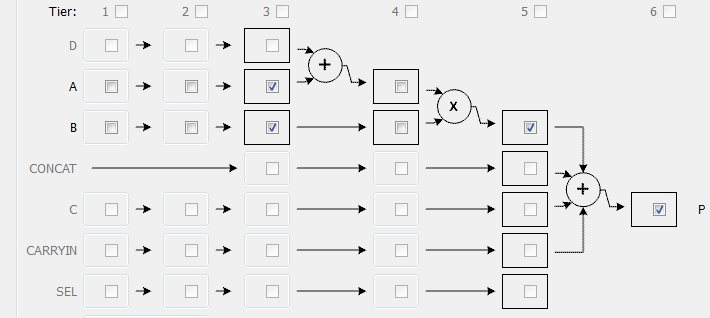

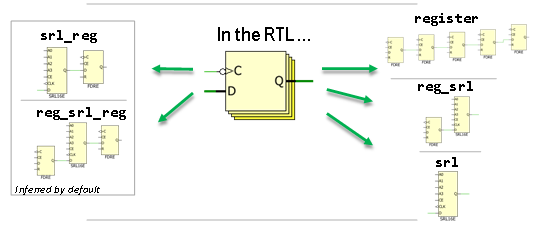

4.6 对Shifter Register的优化

利用Vivado HLS 2014.4的Shift Register RTL Attribute,有5种类型SRL来控制不同的shifter register组合:srl, srl_reg, reg_srl, reg_srl_reg。

比如在Vivado HLS生成的RTL代码中加(* srl_style “reg_srl_reg” *),将综合成在SRL之前、之后分别用一个register来实现。:

5. Vivado HLS QRD矩阵分解设计结果

本文中QRD矩阵分解的大小是128x128的单精度复数浮点,我们使用Xilinx

Vivado HLS 2014.4版本,将其生成的RTL在Xilinx Virtex-7 FPGA上实现。

5.1 延迟(latency)性能

本文所述的设计,在Xilinx Vivado HLS 2014.4中达到的延迟15237个时钟周期。

5.2 Interval(吞吐率的倒数)性能

在Xilinx Vivado HLS中,interval是指下一个新的可以输入QRD模块的数据与前一个数据之间所间隔的时钟周期数,也可以理解为吞吐率的倒数。这里Interval的单位是时钟周期。

本文所述的设计,在Xilinx Vivado HLS 2014.4 中达到的Interval是15238个时钟周期。

5.3 时序(timing)性能

使用Xilinx Vivado HLS 2014.4在Xilinx Virtex-7器件中实现单个128x128单精度浮点复数QRD分解模块,时钟频率达到了350 MHz (2.85ns)。

5.4 处理时间性能

QRD矩阵分解的处理时间就是所用的延迟x时钟周期,所以是:15237 x 2.85 = 43.4 uS。

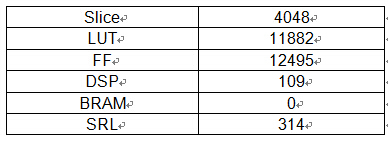

5.5 FPGA资源

将Xilinx Vivado HLS 2014.4生成的RTL代码,在Vivado 2014.4中综合,实现,使用的资源如下表。这个资源使用率只占Xilinx Virtex-7 7V485T的4%,使用Vivado HLS 2014.4高效地实现了QRD矩阵分解。

6. 总结

使用Xilinx Vivado HLS工具,可以让算法工程师、FPGA工程师及软件工程师快速基于FPGA实现典型的数字信号处理算法。本文以浮点复数QRD矩阵分解为例,介绍了如何使用 Vivado HLS 快速、高效地基于FPGA实现,并降低开发者对算法的FPGA实现难度。

Vivado HLS可以帮助设计者大幅提升生产力。 使用 Vivado HLS 开发效率比手写RTL实现快5-10倍,其FPGA资源效率与手写RTL接近,且C/C++仿真验证比传统FPGA RTL要快100倍。

Xilinx公司资深DSP专家王宏强

Xilinx公司高级FAE 徐坚邓涛

Xilinx公司工具与方法学高级专家徐天容

Xilinx中国海量优质的信息资源、行业资讯、最新开发方案等资讯信息平台。