以下是笔者一些关于FPGA功耗估计和如何进行低功耗设计的知识:

买芯片网专注整合全球优质赛灵思代理商现货资源,是国内领先的Altera(英特尔)、Lattice(莱迪思)、Xilinx(赛灵思 AMD)芯片采购服务平台,买芯片网轻松满足您的芯片采购需求.

1. 功耗分析

整个FPGA设计的总功耗由三部分功耗组成:1. 芯片静态功耗;2. 设计静态功耗;3. 设计动态功耗。

芯片静态功耗:FPGA在上电后还未配置时,主要由晶体管的泄露电流所消耗的功耗

设计静态功耗:当FPGA配置完成后,当设计还未启动时,需要维持I/O的静态电流,时钟管理和其它部分电路的静态功耗

设计动态功耗:FPGA内设计正常启动后,设计的功耗;这部分功耗的多少主要取决于芯片所用电平,以及FPGA内部逻辑和布线资源的占用

显而易见,前两部分的功耗取决于FPGA芯片及硬件设计本身,很难有较大的改善。可以优化是第3部分功耗:设计动态功耗,而且这部分功耗占总功耗的90%左右,因此所以降低设计动态功耗是降低整个系统功耗的关键因素。上面也提到过功耗较大会使FPGA发热量升高,那有没有一个定量的分析呢?答案当然是有,如下式:

Tjmax > θJA * PD + TA

其中Tjmax表示FPGA芯片的最高结温(maximum junction temperature);θJA表示FPGA与周围大气环境的结区热阻抗(Junction to ambient thermal resistance),单位是°C/W;PD表示FPGA总功耗(power dissipation),单位是W;TA表示周围环境温度。

以XC7K410T-2FFG900I系列芯片为例,θJA = 8.2°C/W,在TA = 55°C的环境中,想要结温Tjmax不超过100°C的情况下,可以推算FPGA的总功耗:PD (Tjmax – TA)/θJA=(100 - 55)/8.2=5.488W,之前估算的20W与之相差太远,因此优化是必不可少的:

1) 降低θJA:热阻抗取决于芯片与环境的热传导效率,可通过加散热片或者风扇减小热阻抗

图1

2) 减小PD:通过优化FPGA设计,降低总功耗,这也是本文重点讲解的部分。

2. 功耗估计

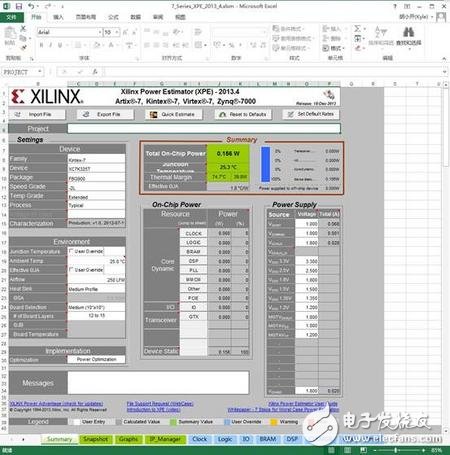

在讲解低功耗设计之前,介绍一下xilinx的功耗估计工具XPE(Xilinx Power Estimator),XPE主要是在项目初期,处于系统设计,RTL代码并未完善阶段功耗估计时使用,它是一个基于EXCEL的工具,,功能做的十分丰富。

图2

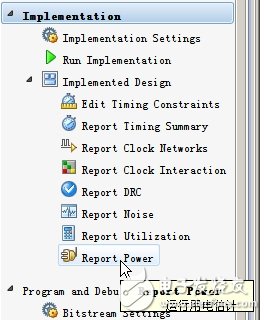

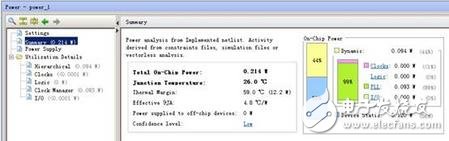

在设计完成综合实现后,则可以使用vivado自带的功耗分析工具进行精确计算功耗。打开综合实现后的设计,点击report power即可得到功耗分析的结果,。

图3

图4

3. 低功耗设计

关于FPGA低功耗设计,可从两方面着手:1) 算法优化;2) FPGA资源使用效率优化。

1) 算法优化

算法优化可分为两个层次说明:实现结构和实现方法

首先肯定需要设计一种最优化的算法实现结构,设计一种最优化的结构,使资源占用达到最少,当然功耗也能降到最低,但是还需要保证性能,是FPGA设计在面积和速度上都能兼顾。比如在选择采用流水线结构还是状态机结构时,流水线结构同一时间所有的状态都在持续工作,而状态机结构只有一个状态是使能的,显而易见流水线结构的功耗更多,但其数据吞吐率和系统性能更优,因此需要合理选其一,使系统能在面积和速度之间得到平衡;

另一个层面是具体的实现方法,设计中所有吸收功耗的信号当中,时钟是罪魁祸首。虽然时钟可能运行在 100 MHz,但从该时钟派生出的信号却通常运行在主时钟频率的较小分量(通常为 12%~15%)。此外,时钟的扇出一般也比较高。这两个因素显示,为了降低功耗,应当认真研究时钟。 首先,如果设计的某个部分可以处于非活动状态,则可以考虑禁止时钟树翻转,而不是使用时钟使能。时钟使能将阻止寄存器不必要的翻转,但时钟树仍然会翻转,消耗功率。其次,隔离时钟以使用最少数量的信号区。不使用的时钟树信号区不会翻转,从而减轻该时钟网络的负载。

2) 资源使用效率优化

资源使用效率优化是介绍一些在使用FPGA内部的一些资源如BRAM,DSP48E1时,可以优化功耗的方法。FPGA动态功耗主要体现为存储器、内部逻辑、时钟、I/O消耗的功耗。

其中存储器是功耗大户,如xilinx FPGA中的存储器单元Block RAM,因此在这边主要介绍对BRAM的一些功耗优化方法。

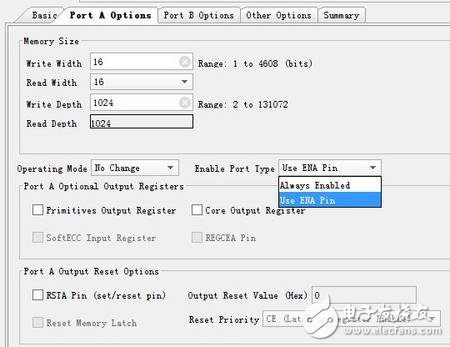

;其中“NO CHANGE”表示BRAM不添加额外的逻辑防止读写冲突,因此能减少功耗,但是设计者需要保证程序运行时不会发生读写冲突。

图6

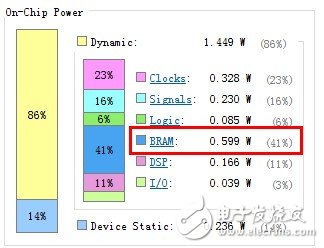

图5中的功耗是设置成“Write First”时的,图7中是设置成“NO CHANGE”后的功耗,BRAM的功耗从0.614W降到了0.599W,因为只使用了7%的BRAM,如果设计中使用了大量的BRAM,效果能更加明显。

图7

b) 控制“EN”信号:BRAM的端口中有clock enable信号,,在端口设置中可以将其使能,模块例化时将其与读/写信号连接在一起,如此优化可以使BRAM在没有读/写操作时停止工作,节省不必要的功耗。

图8

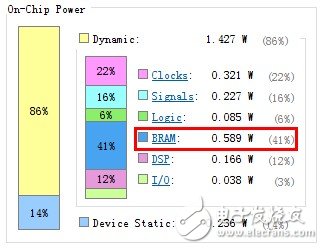

为控制“EN”信号优化后的功耗情况,BRAM功耗降到了0.589W

图9

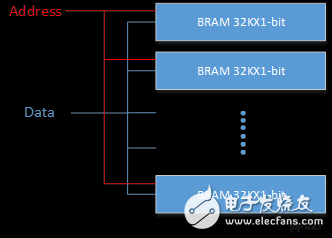

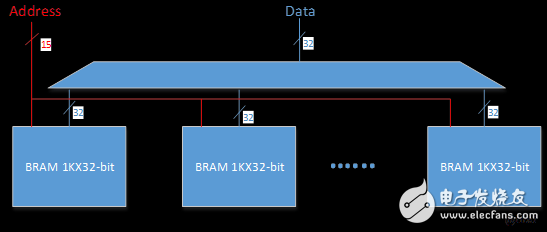

c) 拼深度:当设计中使用了大量的存储器时,需要多块BRAM拼接而成,如需要深度32K,宽度32-bit,32K*32Bit的存储量,但是单块BRAM如何配置是个问题?7 series FPGA中是36Kb 的BRAM,其中一般使用32Kb容量,因此可以配置成32K*1-bit或者1K*32-bit,多块BRAM拼接时,前者是“拼宽度”(见图10),后者是“拼深度”(见图11)。两种结构在工作时,“拼宽度”结构所有的BRAM需要同时进行读写操作;而“拼深度”结构只需要其中一块BRAM进行读写,因此在需要低功耗的情况下采用“拼深度”结构,

注:“拼深度”结构需要额外的数据选择逻辑,增加了逻辑层数,为了降低功耗即牺牲了面积又牺牲了性能。

图10

图11

Xilinx中国海量优质的信息资源、行业资讯、最新开发方案等资讯信息平台。