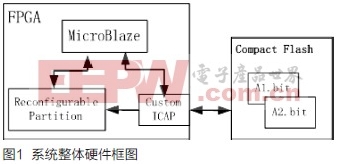

分动态可重构技术中最关键的一个步骤就是比特流文件的下载。传统的下载方法是通过FPGA提供的内部配置访问端口(ICAP),使得内嵌的微处理器能够直接在可编程器件内部对可重构操作进行控制。通过ICAP端口在可重构器件内部对器件进行部分重构的基本步骤是,首先把部分配置数据放在存储器设备上,在重构时,处理器从外部存储器上读取配置数据,然后通过片内的总线将配置数据发送给封装ICAP模块的HWICAP,然后通过HWICAP的控制模块将部分配置数据写入ICAP端口,完成系统自重构的功能。此设计中的HWICAP和ICAP接口都是自行设计,充分解释了其工作过程。

买芯片网专注整合全球优质赛灵思代理商现货资源,是国内领先的Altera(英特尔)、Lattice(莱迪思)、Xilinx(赛灵思 AMD)芯片采购服务平台,买芯片网轻松满足您的芯片采购需求.

整体设计方案

原型系统的整体硬件框图。部分配置文件存放在CF卡中,用户通过超级终端输入重构命令,MicroBlaze处理器读取命令发生重构。重构时,MicroBlaze通过应用程序从CF卡中读取文件,并分析其文件长度,然后通过自定制的ICAP接口将配置信息存到配置存储器中,完成对重构区域的重配置。

整个系统的设计是在Xilinx嵌入式设计套件中实现的,使用的是ISE Design Suite12.4和EDK12.4设计工具,所使用的开发平台是Digilent公司生产的Xilinx Virtex-5 ML505开发板,采用的FPGA器件为XC5VLX110T。

设计流程

在基于模块的部分重构设计流程的基础上,Xilinx公司提出了针对Virtex-4及其以上版本器件的嵌入式设计流程,并在许多地方进行了改进。

Xilinx中国海量优质的信息资源、行业资讯、最新开发方案等资讯信息平台。