作为赛灵思用户论坛的定期访客,我注意到新用户往往对时序收敛以及如何使用时序约束来达到时序收敛感到困惑。为帮助 FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现FPGA 设计的最优结果。

买芯片网专注整合全球优质赛灵思代理商现货资源,是国内领先的Altera(英特尔)、Lattice(莱迪思)、Xilinx(赛灵思 AMD)芯片采购服务平台,买芯片网轻松满足您的芯片采购需求.

何为时序约束?

为保证设计的成功,设计人员必须确保设计能在特定时限内完成指定任务。要实现这个目的,我们可将时序约束应用于连线中——从某 FPGA 元件到 FPGA 内部或 FPGA 所在 PCB 上后续元件输入的一条或多条路径。

在 FPGA 设计中主要有四种类型的时序约束:PERIOD、OFFSET IN、OFFSET OUT 以及 FROM: TO(多周期)约束。

PERIOD 约束与建组

每个同步设计要有至少一个PERIOD 约束(时钟周期规格),这是最基本的约束类型,指定了时钟周期及其占空比。若设计中有不止一个时钟,则每个时钟都有自己的 PERIOD 约束。PERIOD约束决定了我们如何进行布线,来满足设计正常工作的时序要求。

为简化时序约束应用过程,常常可将具有类似属性的连线分组为一组总线或一组控制线。这样做有助于完成正确为设计约束定义优先级这一关键步骤。

设计约束优先次序排列

若设计有多重约束,则需进行优先次序排列。一般来说,约束的一般性越强,其优先级越低。相反,约束的针对性越强,其优先级越高。举例来说,时钟网络上的某个一般性 PERIOD 约束将被特定网络的具有更高优先级的 FROM: TO 约束所覆盖。

特定 FROM: TO(或 FROM: THRU:TO)约束在时钟域内任意网络中的重要性均高于一般性约束。

为便于进行约束的优先级排列,可运行赛灵思时序分析器(ISE® Design Suite中的静态时序分析工具),并生成时序规格迭代报告,即常说的 .tsi 报告。该报告说明了各约束间是如何迭代的,以及该工具如何为各约束设置默认优先级。

采用 PRIORITY 约束关键词可手动设置任一时序约束的优先级并使其优先于默认的或预先设定的优先级。这对同一路径上的两个或多个时序约束发生冲突时尤为有用。这里的优先级指的是同一路径上有两个或多个时序约束时,该应用哪一个。其余的低优先级约束则被忽略。优先级可在 -10 ~ +10 的范围内设置。

PRIORITY 值越低,优先级越高。注意该值不会影响到哪些路径应率先布局和走线,只有当优先级相同的两个约束出现在同一路径上时,它才会影响由哪个约束控制该路径。

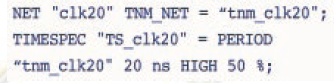

下面将以 PERIOD 只控制从同步元件到同步元件之间的网络,如 FFS 到FFS 为例来进一步介绍(约束以蓝色显示如下):

创建名为 tnm_clk20 的 TIMEGRP(时序分组),包含网络 clk20 驱动的所有下游同步组件。这些同步元件间的所有路径均受时序规格“TS_clk20: 20ns”(同步元件到同步元件 20 纳秒的时间要求)的约束。“HIGH 50%”指 clk20 的占空比为50/50。

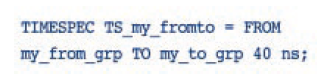

在第二个例子中,我们使用 FROM:TO 约束来定义对两个分组间路径的要求,即:

该命令的作用是告知工具,确保数据从时序分组“my_from_grp”包含的元件到“my_to_grp”的元件所用时间为 40纳秒。时序分析器仍将计算从源分组到目标分组的时钟偏移,不过若时钟关联,则优先级较低。也可使用如下预定义分组:

Xilinx中国海量优质的信息资源、行业资讯、最新开发方案等资讯信息平台。